Hochauflösende, effiziente inkrementelle Sigma-Delta-Modulatoren

Sigma-Delta (ΣΔ) ADCs sind aufgrund ihres Oversampling- und Rauschformungsverhaltens für verschiedene Anwendungen geeignet, so dass unabhängig von der Anpassungsgenauigkeit der analogen Komponenten hohe Auflösungen erreicht werden können. Für Multiplex-Anwendungen, bei denen ein ADC zur Digitalisierung des von mehreren Kanälen kommenden Eingangs verwendet wird, ist eine Sample-by-Sample-Wandlung erforderlich. Ungeachtet der vielen Vorteile von Sigma-Delta-ADCs ist jedes Ausgangssample von dem vorhergehenden abhängig, so dass eine Sample-by-Sample-Wandlung nicht möglich ist. Daher sind ADCs mit Nyquist-Rate (z. B. SAR ADC) im Bereich der Multiplex-Anwendungen vorherrschend.

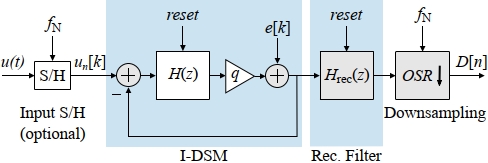

Andererseits haben inkrementelle Sigma-Delta (I-ΣΔ)-ADCs in den letzten Jahren zunehmend an Interesse gewonnen, da sie die grundlegenden Eigenschaften eines frei laufenden ΣΔ-Modulators übernehmen. Durch Zurücksetzen der internen Zustände des Modulators und des nachfolgenden digitalen Filters innerhalb des ADC (Abb. 1) wird jedoch eine Abtastung nach Abtastung und eine echte Nyquist-Rate-Wandlung erreicht. Dadurch können I-ΣΔ-ADCs mit anderen ADCs mit Nyquist-Rate (z. B. SAR-ADCs) konkurrieren und aufgrund ihrer Unempfindlichkeit gegenüber Elementfehlanpassungen hohe Auflösungen erreichen.

Der Bereich der I-ΣΔ-Modulatoren gilt als ein junges Forschungsgebiet mit vielen ungeklärten Phänomenen und einzigartigen Eigenschaften, die sich vom frei laufenden ΣΔ-ADC unterscheiden und ihm einen zusätzlichen Freiheitsgrad verleihen. Daher sind weitere Lösungen und Ideen zur Überwindung der Design-Herausforderungen und zur Erzielung hochauflösender, energieeffizienter Designs sehr erwünscht.

Publikationen

- Kässer, P.; Ismail, O.; Wiens, D.-P.; Ortmanns, M.

Offset Cancellation in Incremental ∆Σ ADCs

IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Mai 2024

DOI: 10.1109/ISCAS58744.2024.10557952 - Kässer, P.; Wagner, J.; Ismail, O.; Ortmanns, M.

Inner Transfer Functions in Incremental ΔΣ ADCs

IEEE Transactions on Circuits and Systems II: Express Briefs, April 2024

DOI: 10.1109/TCSII.2024.3390397 - Ismail, O.; Kässer, P.; Kauffman, J. G.; Ortmanns, M.

Non-Ideal Reset in Incremental Delta-Sigma ADCs

IEEE 22nd Interregional NEWCAS Conference Sherbrooke, Quebec, Canada, April 2024 - Ismail, O.; Kässer, P.; Kauffman, J. G.; Ortmanns, M.

DAC Element Mismatch Shaping Algorithms in Incremental Delta-Sigma ADCs

IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, Januar 2024

DOI: 10.1109/ISCAS58744.2024.10558337 - Kässer, P.; Ismail, O.; Wagner, J.; Fischer, R.; Ortmanns, M.

Frequency-Domain Analysis of Reconfigured Incremental ΔΣ ADCs on the Example of the Exponential Phase

IEEE Transactions on Circuits and Systems I: Regular Papers, September 2023

DOI: 10.1109/TCSI.2023.3310655 - Mokhtar, M. A.; Ismail, O.; Vogelmann, P.; Kauffman, J. G.; Ortmanns, M.

A 40 kS/sCalibration-Free Incremental △Σ ADC Achieving 104 dB DR and 105.7 dB SFDR

ESSCIRC 2023- IEEE 49th European Solid State Circuits Conference (ESSCIRC), Lisbon, Portugal, pp. 401-404, September 2023

DOI: 10.1109/ESSCIRC59616.2023.10268735 - Kässer, P.; Ismail, O.; Rudorf, C.; Wagner, J.; Ortmanns, M.

Linear-Exponential I-DS ADCs: Analysis, Limitations and Higher Order

IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, pp. 1-5, Mai 2023

DOI: 10.1109/ISCAS46773.2023.10182215