Delta-Sigma-Analog-Digital-Wandler mit geringem Stromverbrauch und breiter Bandbreite mit hoher interner Auflösung

Zeitkontinuierliche Delta-Sigma-Modulatoren (CT-DSMs) haben sich in jüngster Zeit zu den wichtigsten Geräten für die drahtlose und drahtgebundene Breitbandkommunikation entwickelt. Aufgrund ihres eingebauten Anti-Aliasing-Filters und der Möglichkeit, die Anforderungen an die Abtastung zu reduzieren, werden CT-DSMs gegenüber ihren zeitdiskreten Pendants bevorzugt.

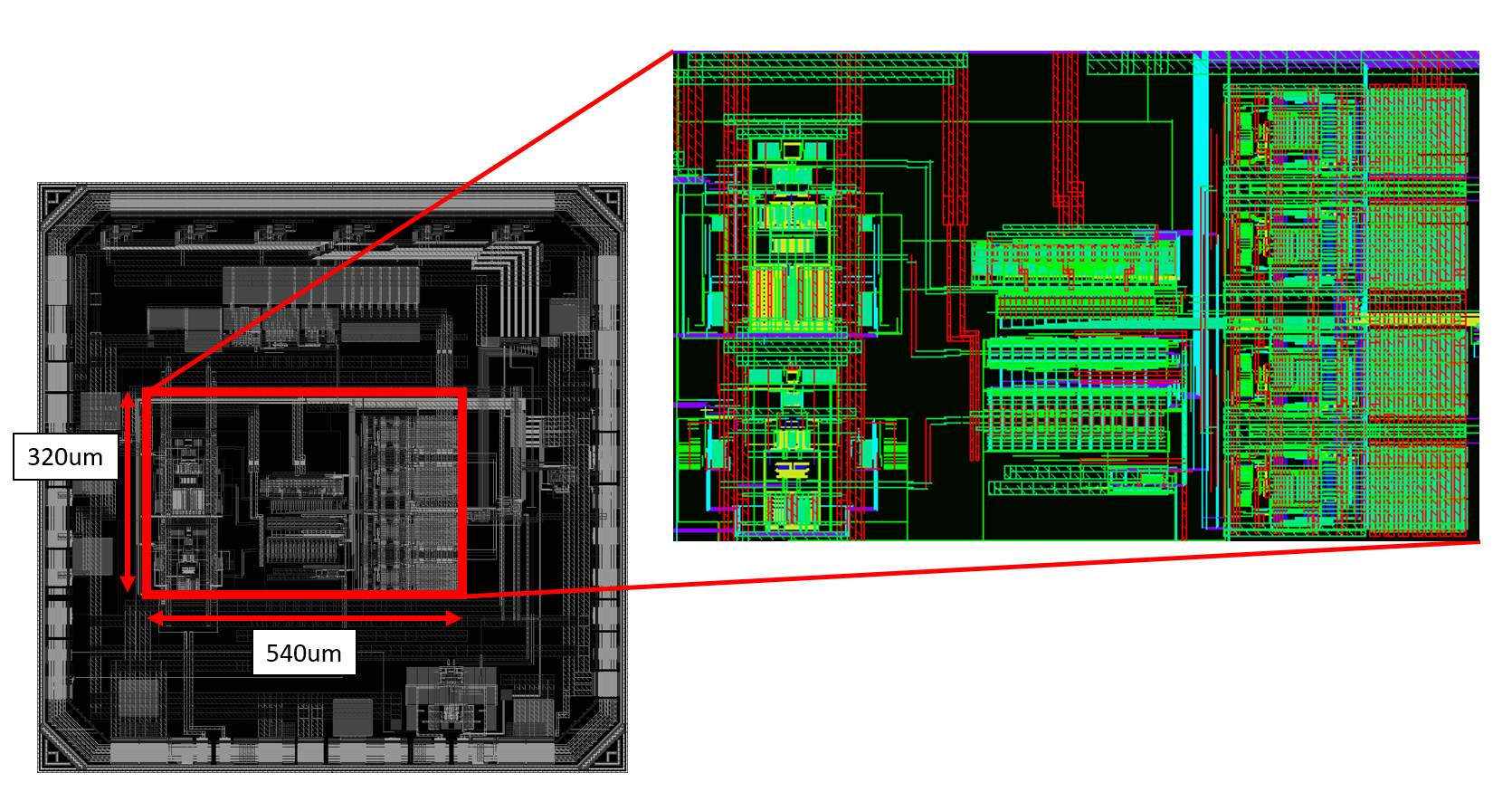

Dieses Projekt konzentriert sich auf den Entwurf, die Entwicklung und den Test von Delta-Sigma-ADCs mit sehr hoher Geschwindigkeit, großer Bandbreite und geringem Stromverbrauch. Einer der wichtigsten Punkte zur Erreichung dieses Ziels ist die Konzentration auf einen hochauflösenden internen Quantisierer. In Kombination mit einem niedrigen Überabtastverhältnis ermöglicht dies eine große Bandbreite, während der Stromverbrauch aufgrund der begrenzten Abtastgeschwindigkeit niedrig bleibt. Die Anwendung spezieller Kompensationstechniken gewährleistet die Stabilität des CT-DSM und eröffnet einen gangbaren Weg, um die Wandlungsraten weiter zu erhöhen und gleichzeitig das FoM unter 100fJ/Wandlung zu halten.

Publikationen

4. Pietzko, M.; Ungethüm, J.; Abdelaal, A.; Kauffman, J. G.; Ortmanns, M.

A 600MS/s 10-bit SAR ADC with unit via-based delta-length C-DAC in 22nm FDSOI

IEEE International Symposium on Circuits and Systems (ISCAS), Singapore

Mai 2024

DOI: 10.1109/ISCAS58744.2024.10558087

3. Pietzko, M.; Spiess, J.; Ungethüm, J.; Kauffman, J. G.; Li, Q.; Ortmanns, M.

Bitwise ELD Compensation under Integrator Nonidealities in ΔΣ Modulators

21st IEEE Interregional NEWCAS Conference (NEWCAS), Edinburgh, United Kingdom

Juni 2023

DOI: 10.1109/NEWCAS57931.2023.10198050

2. Pietzko, M.; Ungethüm, J.; Kauffman, J. G.; Ortmanns, M.

Delay Error Shaping in ΔΣ Modulators Using Time-Interleaved High Resolution Quantizers

IEEE Transactions on Circuits and Systems I: Regular Papers

Mai 2023

DOI: 10.1109/TCSI.2023.3269573

1. Pietzko, M.; Ungethüm, J.; Kauffman, J. G.; Li, Q.; Ortmanns, M.

Bitwise ELD Compensation in ∆Σ Modulators

IEEE International Symposium on Circuits and Systems (ISCAS), Austin, USA

Mai 2022

DOI: 10.1109/ISCAS48785.2022.9937305

Dieses Projekt wird durch die Deutsche Forschungsgesellschaft (DFG) unter Projektnummer OR 245/17-2 gefördert.